Tryb strony zerowej Y

Opis

Tryb adresowania, przy którym adres efektywny jest sumą argumentu i wartości w rejestrze Y.

Na przykład, wykonanie instrukcji asemblerowej LDA $1E,Y, gdzie rejestr Y=$02 spowoduje, że do akumulatora zostanie wczytana wartość pobrana z komórki o adresie $0020. W tej komórce znajduje się liczba $32 i taką wartość przyjmie akumulator po wykonaniu tego rozkazu.

Chociaż procesor 6502 obsługuje szesnastobitowe adresy, w tym adresowaniu jest potrzebny tylko najmłodszy bajt adresu efektywnego, ponieważ starszy jest zawsze równy zero. Strona zerowa, tak jak każda inna strona, ma 256 bajtów. Argument jest numerem bajtu na stronie, z którego ma być pobrana wartość potrzebna do wykonania operacji. Rejestr Y jest w reprezentacji NKB (jego wartość jest zawsze nieujemna).

Tryb ten różni się od adresowania strony zerowej X tylko używanym rejestrem i liczbą obsługiwanych instrukcji. Tylko dwa rozkazy obsługują ten tryb adresowania: LDX i STX.

Rozkazy te zawsze zajmują po dwa bajty ze względu na obecność ośmiobitowego argumentu i liczbą obsługiwanych instrukcji.

Uwaga! Jeśli suma argumentu i wartości w rejestrze Y będzie większa, niż $FF, to najstarszy bajt adresu zostanie wyzerowany i to spowoduje, że zostanie wskazany bajt na stronie zerowej o numerze równym najmłodszemu bajtowi sumy. Adresowanie strony zerowej Y nie obsługuje więc przekroczenia strony.

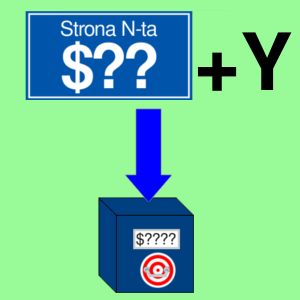

Składnia instrukcji

ROZ - mnemonik

$?? - ośmiobitowa liczba szesnastkowa, będąca najmłodszym bajtem adresu efektywnego

Przykłady zastosowania

LDX $1E, Y STX $2E, Y